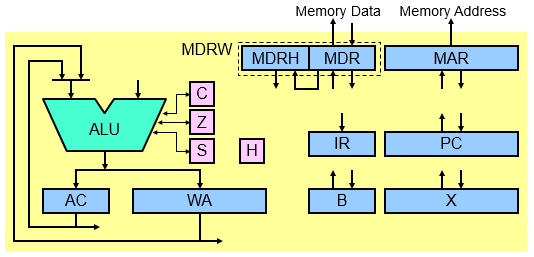

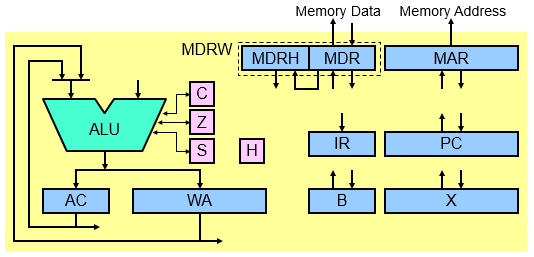

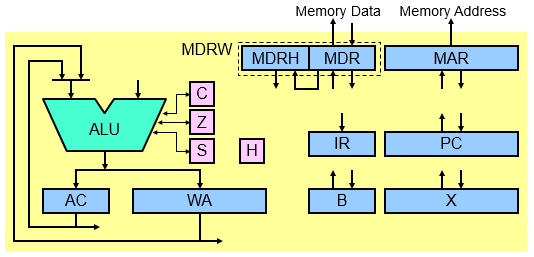

マイクロプロセッサELC-1の構成要素

マイクロプロセッサELC-1には、以下に示す構成要素がある。

|

|

図1. マイクロプロセッサELC-1のアーキテクチャ

|

PC プログラムカウンタ(16ビット)

次に実行する命令を読み出すメモリアドレスが記録されている。

アドレス相対ジャンプのための加算機能がある。

インクリメント(値を1増加)機能がある。

IR 命令レジスタ(8ビット)

メモリから読み出した命令コードが記録されている。

AC アキュムレータ(8ビット)

ALU(算術論理装置)による8ビット演算結果が格納される。

ALUの左入力として使用される。

WA ワイドアキュムレータ(16ビット)

ALU(算術論理装置)による16ビット演算結果が格納される。

ALUの左入力として使用される。

インクリメント(値を1増加)およびデクリメント(値を1減少)機能がある。

ただし、インクリメント、デクリメントはALUを使用せず、フラグも変化しない。

B 汎用レジスタ(8ビット)

任意の8ビットのデータを記憶する。

インクリメント(値を1増加)およびデクリメント(値を1減少)機能がある。

ただし、インクリメント、デクリメントはALUを使用せず、フラグも変化しない。

X 汎用レジスタ(16ビット)

任意の16ビットのデータを記憶する。

インクリメント(値を1増加)およびデクリメント(値を1減少)機能がある。

ただし、インクリメント、デクリメントはALUを使用せず、フラグも変化しない。

MAR メモリアドレスレジスタ(16ビット)

メモリに与えるアドレスデータを格納する。

インクリメント(値を1増加)機能がある。

MDR メモリデータレジスタ(8ビット)

メモリからのデータ読み出しでは、メモリから読み出したデータが格納される。

メモリへのデータ書き込みでは、メモリに書き込むデータをMDRに格納してからメモリ書き込み信号を与える。

MDRH メモリデータレジスタ(8ビット)

以下に述べるMDRWの上位8ビットに対応するレジスタである。

MDRから値を転送して保存することが可能であり、MDRH単独で8ビットデータを読み出すことはできない。

MDRW メモリデータレジスタ(16ビット)

MDRWは16ビットデータを読み出すことだけが可能な仮想レジスタであり、実際に16ビットレジスタが存在するのではない。

MDRWの値を参照(読み出す)場合、上位8ビットはMDRHの値、下位8ビットはMDRの値が使用される。

ALU 算術論理装置(Arithmetic-Logic Unit)

算術演算、論理演算、シフト操作を行う。

上の図に示すように、ALUへの2つの入力のうち、左入力はアキュムレータACまたはWAの内容である。

左入力がACの場合は8ビット処理、WAの場合は16ビット処理を行う。

ALUによる処理結果は、必ずACまたはWAに格納される(例外として、処理結果がどこにも格納されない場合がある)。

左入力・処理内容・結果転送先に応じて以下のようにデータが取り扱われる。

■

ALUが8ビット処理を行う場合

- ALUの左入力がAC(8ビット)の場合は、ALUは常に8ビット処理を行う。

- 例外として、右入力をアキュムレータACに単純転送する場合は、右入力のビット数によらず8ビット処理を行う。

- ALUの右入力は8ビットデータの場合はそのまま、16ビットデータの場合は下位8ビットを使用する。

- 処理結果は8ビットとなる。

- 8ビットの処理結果に基づいてフラグを設定する。

- データ転送先がAC(8ビット)の場合はそのまま転送する。

- データ転送先がWA(16ビット)の場合は、処理内容によって以下のようにデータを16ビットに変換してから転送する。

- 算術演算の場合: 16ビットに符号拡張する。

- 論理演算の場合: 上位8ビットに0を補う。

■

ALUが16ビット処理を行う場合

- ALUの左入力がWA(16ビット)の場合は、ALUは常に16ビット処理を行う。

- 例外として、右入力をアキュムレータWAに単純転送する場合は、右入力のビット数によらず16ビット処理を行う。

- ALUの右入力は16ビットデータの場合はそのまま、8ビットデータの場合は、処理内容によって

以下のようにデータを16ビットに変換してからALUに入力する。

- 算術演算の場合: 16ビットに符号拡張する。

- 論理演算の場合: 上位8ビットに0を補う。

- 処理結果は16ビットとなる。

- 16ビットの処理結果に基づいてフラグを設定する。

- データ転送先がWA(16ビット)の場合はそのまま転送する。

- データ転送先がAC(8ビット)の場合は、処理結果の下位8ビットを転送する。

ALUの処理内容と処理結果に応じて、次に示す状態フラグの値が更新される。

S 符号フラグ(1ビット)

ALUによる演算結果のMSBが'1'の場合にセット(値1が代入)され、MSBが'0'の

場合にリセット(値0が代入)される。

2の補数表現を用いた符号つきデータの場合はMSBは符号ビットとなるので、Sの値によって演算結果の符号(正またはゼロか、負か)を知ることができる。

C 桁上げフラグ(1ビット)

ALUによる加算が桁上げ(carry)を起こした場合、および減算が桁借り(borrow)を起こした場合にセット(値1が代入)される。

また、ALUによるシフト操作により、データのMSBまたはLSBが代入される。

Z ゼロフラグ(1ビット)

ALUによる演算結果がゼロとなる場合にセット(値1が代入)される。それ以外では、リセット(値0が代入)される。

H 停止フラグ(1ビット)

プロセッサの命令実行/停止の状態を制御する。Hの値が1の場合はプロセッサは停止し、次に実行すべき命令の読み出しを行わない。

※注意

アキュムレータAC、レジスタWAの入力にはALUの出力が接続していることと、ALUの一方の入力は常にACの出力またはWAの出力に接続されていること、MDRHの入力はMDRの出力に接続されていること、を除いて、レジスタ間のデータ転送には制約は無い。

つまり、データ転送経路は無数にあり、同時に実行可能なデータ転送数はデータ転送経路数によって制約されることはない。

MAR、MDRはメモリアクセスの際には必ず所要の値によって内容が書き換えられる。

特に、命令フェッチの際にはプログラムカウンタPCの値がMARに転送され、命令コードがメモリからMDRに転送される。

したがって、ある命令から次の命令に進んだときに必ずMARとMDRの内容は書き換えられるので、ある命令で生成したデータを以降の命令で使用したいからといって、そのデータ保存場所としてMARとMDRを用いることはできない。

■メモリ

ELC-1のアドレスビット数は9ビットであり、メモリ空間は512語、アドレスは0(16進数の000)から511(16進数の1FF)までとなる。

レジスタMARの下位9ビットがメモリアドレスとして使用される。

メモリの動作を制御する信号WRがあり、

WR=0のとき読み出し動作、WR=1のとき書き込み動作を行う。

■

メモリアクセス

ELC-1に接続しているメモリのアクセス時間は、ELC-1のクロック周期未満であると仮定してよい。メモリの読み書きは、以下のように行う。

- メモリ読み出し

データを読み出したいメモリアドレスをレジスタMARに転送する。MARの出力はメモリのアドレス入力に接続されており、アドレスをMARに転送してから1クロック以内にデータがメモリから出力される。

したがって、WR=0として、メモリアドレスをMARに転送してから1クロック後にメモリ出力をレジスタMDRに転送すればよい。

- メモリ書き込み

データ書き込み先メモリアドレスをレジスタMARに転送するとともに、書き込むデータをレジスタMDRに転送する。メモリ制御信号WRを1に出力すると、1クロック以内にメモリにデータが書き込まれる。

したがって、アドレスをMARに転送し、データをMDRに転送してからWR=1として少なくとも1クロック待つ必要がある。

|

|

図2. メモリアクセスタイミング

|